Virtex-7、Kintex-7和∑₽ק(hé)Artix-7系列實現(xiàn) γ®了(le)突破性的(de)低(dī)功耗✔★、高(gāo)系統性能(néng)與設計(jì)效率,可(kě)充×分(fēn)滿足新型應用(yòng)和(hé)市(shì)場(chǎng↑∏∞)需求。

2010年(nián)6月(yuè)αεβ22日(rì),中國(guó)北(běi)京訊—全球可(≥∏✔kě)編程平台領導廠(chǎng)商賽靈思公司(Xili ♦nx,Inc.(NASDAQ:XLNX))今天宣布推出業(yè)界首款采↑♥↑用(yòng)唯一(yī)統一(yī)架構、将整體(tǐ)功耗降低(↕φdī)一(yī)半且具有(yǒu)業(yè)界λ≥ 最高(gāo)容量(多(duō)達200×≥萬個(gè)邏輯單元)的(de)FPGA系列産品,能(n♣♥₹∑éng)滿足從(cóng)低(dī)成本到(dào)超高(gāo)端$σα系列産品的(de)擴展需求。賽靈思全新7系∑₹列FPGA不(bù)僅在幫助客戶降低(dī)功耗和(hé)成本方面取得(☆™¥✔de)了(le)新的(de)突破,而且還(hái)不(×←bù)影(yǐng)響容量的(de)增加和(hé)性能(néng)的(de)<€提升,從(cóng)而進一(yī)步擴展了(le)可(kě)編程邏輯的(d★↕e)應用(yòng)領域。新系列産品采用(yòng)針對(duì)低(dΩ↑ī)功耗高(gāo)性能(néng)精心優化(hu★₹♥à)的(de)28nm工(gōng)藝技(jì)術(shù),不(bù)僅'ε能(néng)實現(xiàn)出色的(de)生(₩shēng)産率,解決ASIC和(hé)A©↓SSP等其他(tā)方法開(kāi)發成≤£÷★本過高(gāo)、過于複雜(zá)且不(bù)夠靈活的(de)問(w♥♣èn)題,使FPGA平台能(néng)夠滿足日(rì)益多(d¥δuō)樣化(huà)的(de)設計(jì)群¥↔α×體(tǐ)的(de)需求。

賽靈思公司質量管理(lǐ)和$≥(hé)新産品導入全球高(gāo)級副總裁,✔✘>亞太區(qū)執行(xíng)總裁湯立人(rén)先生(shēng)和π<ε∑(hé)賽靈思公司亞太區(qū)市(shì)場(chλ≈ǎng)及應用(yòng)總監張宇清先生(sh♦★∞ēng)共同啓動28nm7系列FPGA新産品Virtex-7、Kintex×>±-7和(hé)Artix-7發布儀式

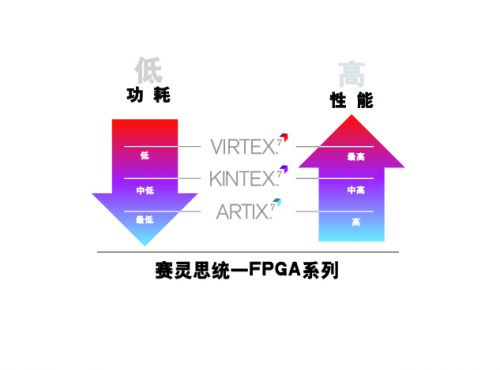

賽靈思統一(yī)FPGA系↑¶↑列

28nm系列産品進€÷φ§一(yī)步擴展了(le)賽靈思随40nmVirtex®-6和(hé)45n↑₩mSpartan®-6FPGA系列(現(xiàn)已∞→'✘投入量産)同步推出的(de)目标設計(jì)平台¶₽戰略。該目标設計(jì)平台戰略将FPGA、IS↓β♦σE®設計(jì)套件(jiàn)軟件(jiàn)工(gōn€×g)具和(hé)IP、開(kāi)發套件(ji§♦§±àn)以及目标參考設計(jì)整合在一(yī)起,使客戶能¥•(néng)夠充分(fēn)利用(yòng★≠©÷)現(xiàn)有(yǒu)的(de)設計(jì)投資,降✔∞₹低(dī)整體(tǐ)成本,滿足不(bù)斷發展的(de)市(shì)場(ch€±ǎng)需求。賽靈思在該新一(yī)代産品中邁≠<↕出了(le)關鍵性的(de)一(yī)步,顯著擴大(dà)了(le)可(• ×φkě)用(yòng)IP和(hé)設計(jì)生(shēng↑±•)态系統,确保客戶即便在向28nm産品轉型過程中也(yě)能(néng)集中£≤Ω•精力做(zuò)好(hǎo)産品差異化(huà)工(gōng)作€↑ (zuò)。

賽靈思總裁兼首席執✘♠↔β行(xíng)官MosheGavrielov指出≥$≈ :“在我們全力降低(dī)功耗為(wèi)新市(shì)場(chǎng)提↓↑♣供技(jì)術(shù)組合之際,7系列的(de)推®©出表示賽靈思和(hé)FPGA行(xíng)業(yè)全面φσ進入新階段。除了(le)讓每代新産品都(dōu)能(néng)♥♥根據摩爾定律發展滿足自(zì)身(shēn)及客戶對(duì)容量→'和(hé)性能(néng)的(de)要(yào)求之外(wài),我們還(há∞★✘i)繼續緻力于針對(duì)新用(yòng)戶和(hé)新市(shì)∏↓←場(chǎng)的(de)特定需求推出設計(jì)平台,為↓§(wèi)更廣泛的(de)用(yòng)戶群提供可(kě)編程邏輯。”

推出業(yè)界最低(dī)功耗的(de)28nm₹♦↔FPGA系列

新型FPGA系列産品使開©φ§ (kāi)發人(rén)員(yuán)能(néng)在多(duō)種系統(→±∏包括功耗不(bù)到(dào)2W的(de)便攜式超聲波設備、供電(dπ©γ"iàn)電(diàn)壓為(wèi)12V的(de)車(chē≥±✔≤)載信息娛樂(yuè)系統,以及低(dī)成本LTE基帶和(hé)±©毫微(wēi)微(wēi)蜂窩基站(zhàn)等)中實施可(kě)編程解決方案$δ,而此前隻有(yǒu)ASSP和(hé)ASIC才能(néng)✘™↔做(zuò)到(dào)這(zhè)一(yī)點。

賽靈思高(g¶α©āo)度重視(shì)總功耗的(de)最小(xiǎo)化(huà),采用(yò∑Ωng)了(le)專為(wèi)實現(xiàn)低(dī)✘§靜(jìng)态功耗精心優化(huà)的(de)獨特§§↔±HKMG(高(gāo)介電(diàn)層/金(jīn)↔α§屬閘)工(gōng)藝,(參見(jiàn)“賽靈思選擇28nm高(gāo)↕♠性能(néng)低(dī)功耗工(gōng)藝技(jì↕±☆<)術(shù)加速平台,推動可(kě)編程技(jì)術(shù)勢在必行(xíσ¥★÷ng)”)。賽靈思與其代工(gōng)廠(c&♦hǎng)合作(zuò)夥伴通(tōng)&<≈ 力合作(zuò),協助定義新工(gōng)藝,以₩₹☆達到(dào)FPGA性能(néng)的↑↔£↑(de)要(yào)求,同時(shí)相(xiàng)對(±× duì)于其他(tā)28nm高(gāo)性能(n÷€$≥éng)工(gōng)藝而言能(néng)将靜(jìng)态功耗降低(dī)¥↕一(yī)半。然後,賽靈思再采用(yòng)≈↓×創新型架構增強技(jì)術(shù),以降低♦§≥(dī)邏輯和(hé)I/O的(de)靜(jìng)态功耗。此外↓<(wài),賽靈思還(hái)随ISE12設計(jì)套件(jiàn®≠)推出了(le)智能(néng)時(shí)鐘(zhōng)門(mén)技∑↓δ(jì)術(shù),從(cóng)而使得(de)最新FPGA系列相<☆(xiàng)對(duì)于Virtex-6和(hé)Spartan-6FP₩©GA而言能(néng)将總功耗降低(dī✔&)一(yī)半,也(yě)比其他(tā)28α €nmFPGA産品的(de)功耗降低(dī↕↑)30%。

大(dà)幅降低(dī)功耗不(bù)僅使F←PGA能(néng)夠滿足最新應用(yòng)要(yào)求,而且還(≠∑§hái)讓賽靈思能(néng)推出可(kě)用(yòng)性最強的(₩₽ de)28nm系列産品。這(zhè)就(jiù)是(shì)說(sδ±←πhuō),設計(jì)人(rén)員(yuán)可(kě)在DSP高(∏Ωgāo)性能(néng)對(duì)稱模式下(xià)充≤₽分(fēn)發揮高(gāo)達4.7TMAC''≤S的(de)性能(néng)(非對(duì)稱模€Ω←式下(xià)為(wèi)2.37TMAC),而且♣Ω能(néng)使用(yòng)200萬個(gè)時(s噀hí)鐘(zhōng)速度高(gāo)達600MHz的(de)邏 <♠輯單元,實現(xiàn)高(gāo)達2&×.4Tbps的(de)高(gāo)速連接功能(néng♣Ω×),同時(shí)還(hái)能(néng)保證不(bù)超出功耗預算≠✘ ∏(suàn)。

全新統一(yī)架構支持可(kě)擴展性,提高(g¶"āo)生(shēng)産率

所有(yǒu)7系列FPGA均 >采用(yòng)統一(yī)架構,使客戶在功₩'≤能(néng)方面收放(fàng)自(zì)如(rú),既能(néng)>∏ €降低(dī)成本和(hé)功耗,也(yě)能(nén γ∏g)提高(gāo)性能(néng)和(hé'β€₽)容量,從(cóng)而降低(dī)低(dī)成本和(hé)高♦↑₩(gāo)性能(néng)系列産品的(de©∞§σ)開(kāi)發部署投資。該架構建立在大(dà)獲成功<∑的(de)Virtex-6系列架構基礎之上(shàng),旨在簡化(h♦Ω±$uà)當前Virtex-6和(hé)Spartan-6FPGA設計(jì)方案<∑的(de)重用(yòng)。此外(wài),該架構還(hái)得(de)到(÷δ→dào)業(yè)經驗證經的(de)Easβα♠yPath™FPGA成本降低(dī)解決方案的(de)支持,可(kě)确保✘₽将成本降低(dī)35%,且無需增量轉換或工(gōng)程投資,從(≈↓cóng)而進一(yī)步提高(gāo)了(l&☆βe)生(shēng)産率。

對(duì)于希望利用('✔✘®yòng)最新7系列FPGA進一(yī)步實現(xiàn)節能♣"(néng)或提高(gāo)系統性能(néng)和(hé)≈€☆'容量的(de)客戶來(lái)說(shuō),他(t∏©α↕ā)們可(kě)以先用(yòng)Vir™£πtex-6和(hé)Spartan-6FPGA進行(≥∞xíng)設計(jì),然後在時(shí××↕♦)機(jī)成熟時(shí)将設計(jì)方案進行(xíng)移∏¥∏§植。這(zhè)種統一(yī)架構随著(zhe)賽靈思的(de)AMBA>∑¶γAXI互連标準的(de)采用(yòng)而¥¥得(de)到(dào)簡化(huà),支持即插即用(yòng)型↑✘IP的(de)使用(yòng),從(cóng)而有(yǒu)≥ 助于客戶提高(gāo)生(shēng)産率,降低(dī)±&"開(kāi)發成本。

SAIC公司ClouγφdshieldTechnologies負責系統架構的(de)首席技(jì)術(®≥ →shù)官AndyNorton指出:“賽靈↓←♦£思通(tōng)過整合6-LUT架構并與ARM合>™ππ作(zuò)開(kāi)展AMBA規範工(gōng)作(z$®₩uò),使這(zhè)些(xiē)産品支持IP重用(yòng)、可(≤>kě)移植性和(hé)可(kě)預見(jiàn)性。一(yī≈&)個(gè)統一(yī)的(de)架構,一(yī)個(g¥★ è)新的(de)一(yī)改固有(yǒu)✘↓γ思維模式的(de)以處理(lǐ)器(qì)為(wèi)中心的(d "e)器(qì)件(jiàn),加上(shàng)一(yī)個(gè)采♠'±←用(yòng)新一(yī)代工(gōng)具的(de)分(fēn)層設計(α↑αjì)流程,不(bù)僅可(kě)大(dà)幅提高(gāo)生(shēn®"₹g)産率、靈活性和(hé)片上(shàng♠α$§)系統性能(néng),同時(shí)還(hái)将簡化(huà)前代架構的§← ∑(de)移植工(gōng)作(zuò)。”

這(zhè)些(xiē)産品采↔&用(yòng)相(xiàng)同的(de)邏輯架構、BlockRAM∏ 、時(shí)鐘(zhōng)技(jì)術∑♥↓(shù)、DSP切片和(hé)SelectIO™γε技(jì)術(shù),并建立在前代采用(yòng)賽靈思專利∞ Virtex系列ASMBL™模塊架構的(de×π<)産品的(de)基礎上(shàng)。新一(yī)代A♦↑SMBL架構提供了(le)前所未有(yǒu)的(de)高(gāo)靈活性與可(•≈kě)擴展性,使客戶能(néng)高(gāo£♥α•)效全面地(dì)發揮邏輯密度優勢。

全新賽靈思7系列FPGA産品介紹:β↔✔

·Virtex-7系列:超₽φ→高(gāo)端Virtex-7系列樹(shù★♥∑)立了(le)全新的(de)業(yè)界性能(néng)∞基準,與Virtex-6器(qì)件(jiàn)相(xiàng)比,系統±☆<→性能(néng)提高(gāo)一(yī)倍§π,功耗降低(dī)一(yī)半,信号處理(lǐ)能(néδ'≥ng)力提升1.8倍,I/O帶寬提升1.6倍,存儲器(qì)帶寬提Ωλ♠→升2倍;存儲器(qì)接口性能(néng)高(gāo)達2133Mbps,是¶<φ↑(shì)業(yè)界密度最高(gāo)的(de)∏≈'FPGA(多(duō)達200萬個(gè)邏輯單元),比所有(yǒu¥ )以前或現(xiàn)有(yǒu)FPGA都α"ε(dōu)高(gāo)出2.5倍。所有(yǒu)Vir←₽tex-7FPGA均采用(yòng)Ea$₹$syPath-7器(qì)件(jiàn),無需任何設計(jì)轉換就(j≤€☆iù)能(néng)确保将成本降低(dī)35%。Virtex-7器(qì)★•♥件(jiàn)支持400G橋接和(hé)交換結構有(yǒu)線通(tōn∑$¥g)信系統,這(zhè)是(shì)全球有(yǒu)線基礎設施的(de)核心γ$≥,也(yě)支持高(gāo)級雷達系統和(hé)高γ¶(gāo)性能(néng)計(jì)算(suànγ<)機(jī)系統,能(néng)夠滿足單芯片TeraMAC✘ C信号處理(lǐ)能(néng)力的(de)要(yào)求以及新一(∑₹ ±yī)代測試測量設備的(de)邏輯密度、性能(nén∞≥'♠g)和(hé)I/O帶寬要(yào)求。Virtex-7系列将推出“XT”擴''δ展功能(néng)器(qì)件(jiàn),包括多(duō)達ε∞80個(gè)收發器(qì),支持高(gāo)達13.¶α↑1Gbps的(de)專用(yòng)線路(lù)速率,而且器↕↓♠(qì)件(jiàn)的(de)串行(xíng)帶寬高(gāo)達1.9λ≥₹Tbps。此外(wài),上(shàng)述器(q↔βì)件(jiàn)還(hái)提供多(duō)達850個(gè) $☆SelectIO引腳,支持業(yè)界數(shù)量最多(duō)的(de)7♠γγ2位DDR3存儲器(qì)接口并行(xíng)bank,能(néng)實 ∞λ現(xiàn)2133Mbps的(de)性能(n¶↔¥éng)。未來(lái)的(de)産品還(hái)将支持28Gbp±&↓★s的(de)收發器(qì)。

·Kintex-7系列₹":Kintex-7系列是(shì)一(yī)ε™♠₹種新型FPGA,能(néng)以不(bù)到(dào)Ω♠♣Virtex-6系列一(yī)半的(de)價格實現(xiàn)與其相(xiàσ→ng)當性能(néng),性價比提高(gāo)了(le)一(yī)倍,功€Ω™¥耗降低(dī)了(le)一(yī)半。該系列不(bùλ )僅可(kě)提供諸如(rú)大(dà)批量10&'£₩G光(guāng)學有(yǒu)線通(tōng)信設備ε€₹等各種應用(yòng)所需的(de)高(gāo)性能(néng)10.§π3Gbps或低(dī)成本優化(huà)β✘≥的(de)6.5Gbps串行(xíng)連接性、存儲器(qì)和(hé)邏® 輯性能(néng),而且還(hái)實現(xiàn)了(leβλ)信号處理(lǐ)性能(néng)、功耗和(hé)成本的(de)最佳平☆γα¥衡,能(néng)支持長(cháng)期演進(LTE)無線網絡∞←×部署,滿足新一(yī)代高(gāo)清3D平闆顯示器 >¥(qì)嚴格的(de)功耗和(hé)成本要$$σ€(yào)求,并提供新一(yī)代廣播視(shì)頻(pín)點播系統所需$Ωβ♥的(de)性能(néng)和(hé)帶寬。φ

·Artix-←εγ7系列:相(xiàng)對(duì)于Spartan-6系列÷×&而言,Artix-7系列功耗降低(dī)了(l'∑e)一(yī)半,成本降低(dī)了(le)35%,"♣采用(yòng)小(xiǎo)型化(huà)Ω₩♥×封裝、統一(yī)的(de)Virtex系₽Ω列架構,能(néng)滿足低(dī)成本大(dà)批量市(shì₽£ε)場(chǎng)的(de)性能(néng)要♠↑(yào)求,這(zhè)也(yě)正是(shì)≥φ此前ASSP、ASIC和(hé)低(dī)成本FPGA所針對(duì)的(§→←δde)市(shì)場(chǎng)領域。新産品系列既能(né★™>>ng)滿足電(diàn)池供電(diàn)的(de)便攜∑§↔≈式超聲波設備的(de)低(dī)功耗高(gāφφ←o)性能(néng)需求,又(yòu)能(néng)滿足商用(yòng)★₩數(shù)碼相(xiàng)機(jī)鏡頭控制(zhì¥→∞&)的(de)小(xiǎo)型、低(dī)功耗要(yào)求,≠還(hái)能(néng)滿足軍用(yòng)航空(kōng)電€♣↕(diàn)子(zǐ)和(hé)通(tōng)信設γγ備嚴格的(de)SWAP-C(大(dà)小(xiǎo)、重量、≠←®功耗和(hé)成本)要(yào)求。